# SURENOO GRAPHIC OLED SERIES DISPLAY Product Specification

(Preliminary)

Part Name: OEL Display Panel SOG240128A P337

Please click the following image to buy the sample

**Business Card**

**Wechat Card**

Shenzhen Surenoo Technology Co.,Ltd.

www.surenoo.com E-mail: info@surenoo.com Skype: Surenoo365

**Graphic OLED Display Selection Guide**

**SSD1322**

www.surenoo.com - 01 -

# **PRODUCT CONTENTS**

- n PHYSICAL DATA

- n absolute maximum ratings

- n EXTERNAL DIMENSIONS

- n ELECTRICAL CHARACTERISTICS

- n TIMING OF POWER SUPPLY

- n ELECTRO-OPTICAL CHARACTERISTICS

- n INTERFACE PIN CONNECTIONS

- n COMMAND TABLE

- n INITIALIZATION CODE

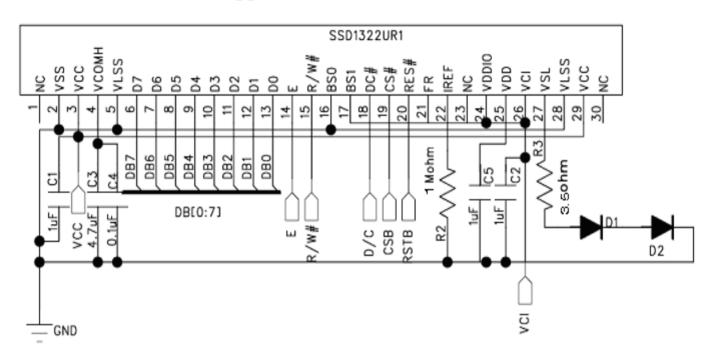

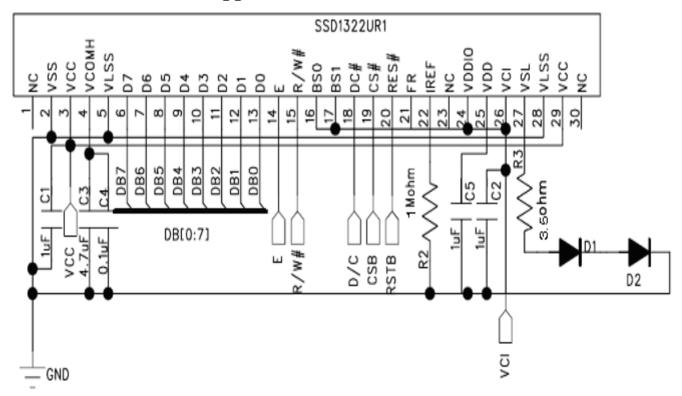

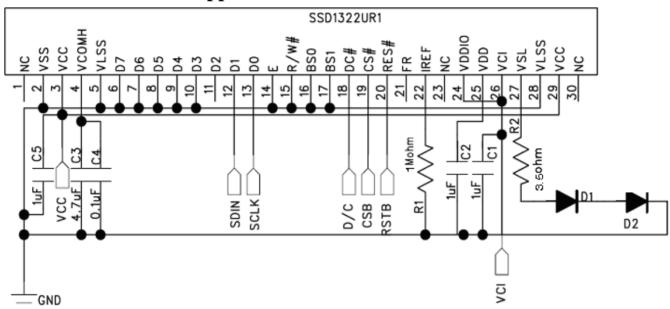

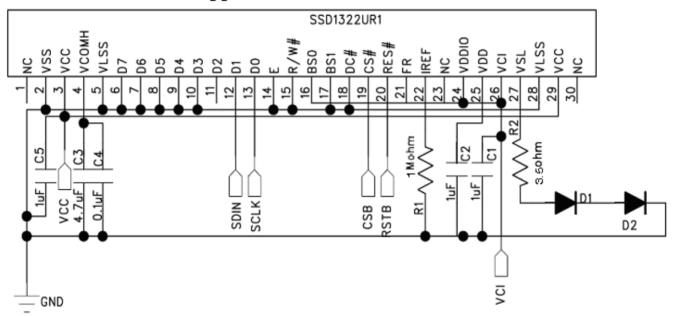

- n SCHEMATIC EXAMPLE

- n RELIABILITY TESTS

- n OUTGOING QUALITY CONTROL SPECIFICATION

- n CAUTIONS IN USING OLED MODULE

www.surenoo.com - 02 -

# **REVISION HISTORY**

| Rev. | Contents                                                               | Date       |

|------|------------------------------------------------------------------------|------------|

| 1.0  | First Release                                                          | 2012-03-20 |

| 1.1  | Update Electro-optical Characteristics and Initialization Code         | 2012-06-06 |

| 1.2  | Update Absolute Maximum Ratings                                        | 2012-11-07 |

| 1.3  | Update the Electro-optical Characteristics and the External Dimensions | 2014-07-26 |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

|      |                                                                        |            |

www.surenoo.com - 03 -

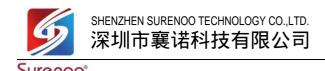

#### n PHYSICAL DATA

| No. | Items:                    | Specification:        | Unit            |

|-----|---------------------------|-----------------------|-----------------|

| 1   | Diagonal Size             | 3.37                  | Inch            |

| 2   | Resolution                | 240(H) x 128(V)       | Dots            |

| 3   | Active Area               | 75.58 (W) x 40.30(H)  | mm <sup>2</sup> |

| 4   | Outline Dimension (Panel) | 89.52 (W) x 54.41(H)  | mm <sup>2</sup> |

| 5   | Pixel Pitch               | 0.315 (W) x 0.315(H)  | mm <sup>2</sup> |

| 6   | Pixel Size                | 0.290 (W) x 0.290 (H) | mm <sup>2</sup> |

| 7   | Driver IC                 | SSD1322Z2             | -               |

| 8   | Display Color             | Yellow                | -               |

| 9   | Grayscale                 | 4                     | Bit             |

| 10  | Interface                 | Parallel / Serial     | -               |

| 11  | IC package type           | COG with ZIF tail     | -               |

| 12  | Thickness                 | $2.05 \pm 0.2$        | mm              |

| 13  | Weight                    | 20                    | g               |

| 14  | Duty                      | 1/128                 | -               |

#### n ABSOLUTE MAXIMUM RATINGS

Unless otherwise specified,  $V_{SS} = 0V$

$(Ta = 25^{\circ}C)$

| I                 | tems        | Symbol              | Min  | Тур. | Max      | Unit                   |

|-------------------|-------------|---------------------|------|------|----------|------------------------|

|                   | I/O         | $V_{\mathrm{DDIO}}$ | -0.5 | -    | $V_{CI}$ | V                      |

| Supply<br>Voltage | Logic       | $V_{CI}$            | -0.3 | -    | 3.6      | V                      |

|                   | Driving     | $V_{CC}$            | -0.5 | -    | 21.0     | V                      |

|                   | Core Logic  | $V_{\mathrm{DD}}$   | -0.5 | -    | 2.75     | V                      |

| Operating '       | Temperature | Top                 | -30  | -    | 80       | $^{\circ}\!\mathbb{C}$ |

| Storage Te        | mperature   | Tst                 | -40  | -    | 85       | $^{\circ}\!\mathbb{C}$ |

| Humidity          | umidity     |                     | -    | -    | 90       | %RH                    |

#### Note:

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

www.surenoo.com - 04 -

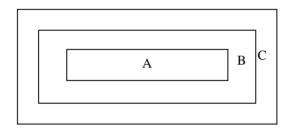

# Display

# n EXTERNAL DIMENSIONS

# n ELECTRICAL CHARACTERISTICS

#### **◆DC** Characteristics

Unless otherwise specified,  $V_{SS} = 0V$ ,  $V_{CI} = 2.4V$  to 3.5V.

$(Ta = 25^{\circ}C)$

|         | Items                        | Symbol              | Min                    | Тур. | Max                             | Unit |

|---------|------------------------------|---------------------|------------------------|------|---------------------------------|------|

|         | I/O                          | $V_{\mathrm{DDIO}}$ | 1.65                   | -    | $V_{CI}$                        | V    |

| Supply  | Logic                        | $V_{CI}$            | 2.4                    | 3.0  | 3.5                             | V    |

| Voltage | Operating                    | $V_{CC}$            | 10.0                   | 14.0 | 20.0                            | V    |

|         | Core Logic                   | $V_{DD}$            | 2.4                    | -    | 2.6                             | V    |

| Input   | High Voltage                 | $V_{IH}$            | $0.8 \times V_{DDIO}$  | -    | $V_{ m DDIO}$                   | V    |

| Voltage | Low Voltage                  | $V_{ m IL}$         | 0                      | -    | $0.2 \text{ x V}_{\text{DDIO}}$ | V    |

| Output  | High Voltage V <sub>OH</sub> |                     | 0.9x V <sub>DDIO</sub> | -    | $V_{ m DDIO}$                   | V    |

| Voltage | Low Voltage                  | $V_{OL}$            | 0                      | -    | $0.1 \text{ x V}_{\text{DDIO}}$ | V    |

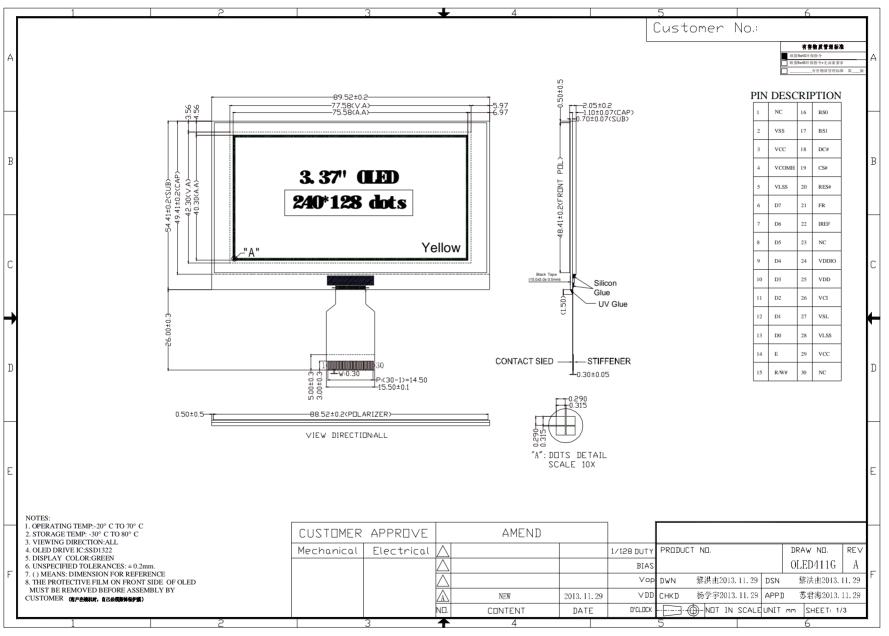

# **♦**AC Characteristics

# Use 8080/6800-Series MPU Parallel Interface or Serial Interface

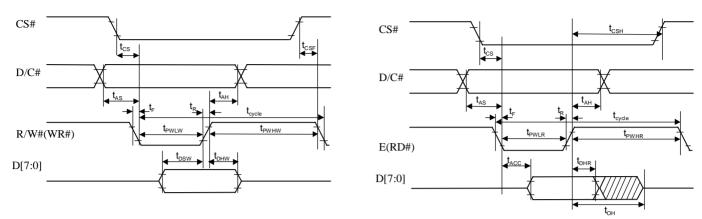

#### 1. 6800 Series MPU Parallel Interface

$(V_{DDIO} - V_{SS} = 1.65 \text{V} - 2.1 \text{V}, V_{CI} - V_{SS} = 2.4 \text{V} - 3.5 \text{V}, T_{A} = 25^{\circ}\text{C})$

| Symbol             | Parameter                                                                | Min        | Тур | Max | Unit |

|--------------------|--------------------------------------------------------------------------|------------|-----|-----|------|

| $t_{CYCLE}$        | Clock Cycle Time (read) Clock Cycle Time (write)                         | 400<br>100 | -   | -   | ns   |

| $t_{AS}$           | Address Setup Time                                                       | 20         | -   | -   | ns   |

| $t_{AH}$           | Address Hold Time                                                        | 0          | -   | -   | ns   |

| $t_{ m DSW}$       | Write Data Setup Time                                                    | 40         | -   | -   | ns   |

| $t_{ m DHW}$       | Write Data Hold Time                                                     | 10         | -   | -   | ns   |

| $t_{\mathrm{DHR}}$ | Read Data Hold Time                                                      | 20         | -   | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                                                      | -          | -   | 70  | ns   |

| t <sub>ACC</sub>   | Access Time                                                              | -          | -   | 200 | ns   |

| $PW_{CSL}$         | Chip Select Low Pulse Width (read) Chip Select Low Pulse Width (write)   | 450<br>60  | -   | -   | ns   |

| PW <sub>CSH</sub>  | Chip Select High Pulse Width (read) Chip Select High Pulse Width (write) | 60<br>60   | -   | -   | ns   |

| $t_R$              | Rise Time                                                                | _          | -   | 15  | ns   |

| $t_{\rm F}$        | Fall Time                                                                | -          | -   | 15  | ns   |

www.surenoo.com - 06 -

#### 2. 8080 Series MPU Parallel Interface

$(V_{DDIO} - V_{SS} = 1.65V - 2.1V, V_{CI} - V_{SS} = 2.4V - 3.5V, T_{A} = 25^{\circ}C)$

| Symbol              | Parameter                            | Min | Тур   | Max | Unit |

|---------------------|--------------------------------------|-----|-------|-----|------|

| t <sub>CYCLE</sub>  | Clock Cycle Time (read)              | 400 | - J P | -   | ns   |

| CICLE               | Clock Cycle Time (write)             | 100 |       |     |      |

| t <sub>AS</sub>     | Address Setup Time                   | 10  | -     | -   | ns   |

| $t_{AH}$            | Address Hold Time                    | 0   | -     | -   | ns   |

| $t_{DSW}$           | Write Data Setup Time                | 40  | -     | -   | ns   |

| $t_{ m DHW}$        | Write Data Hold Time                 | 10  | -     | -   | ns   |

| $t_{\mathrm{DHR}}$  | Read Data Hold Time                  | 20  | -     | -   | ns   |

| $t_{OH}$            | Output Disable Time                  | -   | -     | 70  | ns   |

| $t_{ACC}$           | Access Time                          | -   | -     | 220 | ns   |

| $t_{PWLR}$          | Read Low Time                        | 200 | -     | -   | ns   |

| $t_{PWLW}$          | Write Low Time                       | 60  | -     | -   | ns   |

| $t_{PWHR}$          | Read High Time                       | 60  | -     | -   | ns   |

| $t_{\mathrm{PWHW}}$ | Write High Time                      | 60  | -     | -   | ns   |

| $t_R$               | Rise Time                            | ı   | -     | 15  | ns   |

| $t_{\rm F}$         | Fall Time                            | -   | -     | 15  | ns   |

| $t_{CS}$            | Chip select setup time               | 0   | -     | -   | ns   |

| $t_{CSH}$           | Chip select hold time to read signal | 0   | -     | -   | ns   |

| $t_{CSF}$           | Chip select hold time                | 20  | -     | -   | ns   |

www.surenoo.com - 07 -

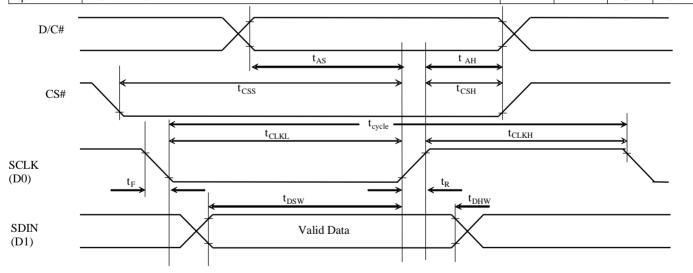

# 3. 4-Wire Serial Interface

$(V_{DDIO} - V_{SS} = 1.65V - 2.1V, V_{CI} - V_{SS} = 2.4V - 3.5V, T_{A} = 25^{\circ}C)$

|                 | (                      | /   |     |     |      |

|-----------------|------------------------|-----|-----|-----|------|

| Symbol          | Parameter              | Min | Тур | Max | Unit |

| $t_{\rm cycle}$ | Clock Cycle Time       | 300 | -   | -   | ns   |

| $t_{AS}$        | Address Setup Time     | 15  | -   | -   | ns   |

| $t_{AH}$        | Address Hold Time      | 35  | -   | -   | ns   |

| $t_{CSS}$       | Chip Select Setup Time | 20  | -   | -   | ns   |

| $t_{CSH}$       | Chip Select Hold Time  | 10  | -   | -   | ns   |

| $t_{ m DSW}$    | Write Data Setup Time  | 15  | -   | -   | ns   |

| $t_{ m DHW}$    | Write Data Hold Time   | 20  | -   | -   | ns   |

| $t_{CLKL}$      | Clock Low Time         | 40  | -   | -   | ns   |

| $t_{CLKH}$      | Clock High Time        | 40  | -   | -   | ns   |

| $t_R$           | Rise Time              | -   | -   | 15  | ns   |

| $t_{\rm F}$     | Fall Time              | -   | -   | 15  | ns   |

www.surenoo.com - 08 -

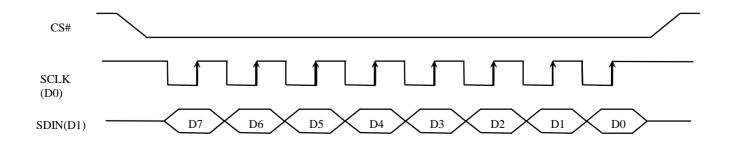

#### 4. 3-Wire Serial Interface

$(V_{DDIO} - V_{SS} = 1.65V - 2.1V, V_{CI} - V_{SS} = 2.4V - 3.5V, T_{A} = 25^{\circ}C)$

| Symbol         | Parameter              | Min | Тур | Max | Unit |

|----------------|------------------------|-----|-----|-----|------|

| $t_{ m cycle}$ | Clock Cycle Time       | 300 | -   | -   | ns   |

| $t_{CSS}$      | Chip Select Setup Time | 20  | -   | -   | ns   |

| $t_{CSH}$      | Chip Select Hold Time  | 35  | -   | -   | ns   |

| $t_{ m DSW}$   | Write Data Setup Time  | 15  | -   | -   | ns   |

| $t_{ m DHW}$   | Write Data Hold Time   | 20  | -   | -   | ns   |

| $t_{ m CLKL}$  | Clock Low Time         | 40  | -   | _   | ns   |

| $t_{CLKH}$     | Clock High Time        | 25  | -   | _   | ns   |

| $t_{R}$        | Rise Time              | -   | -   | 15  | ns   |

| $t_{\rm F}$    | Fall Time              | -   | -   | 15  | ns   |

www.surenoo.com - 09 -

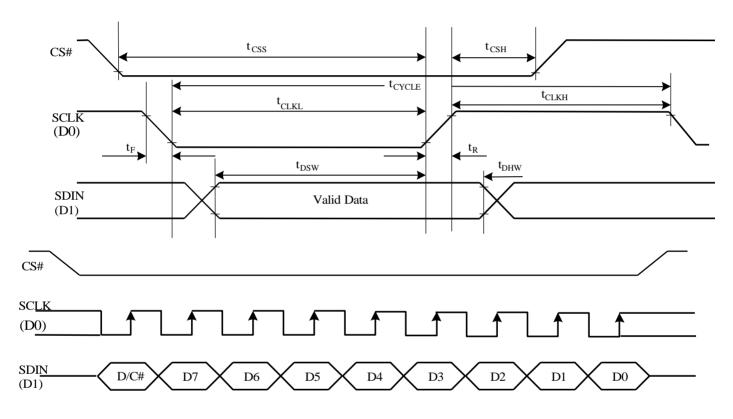

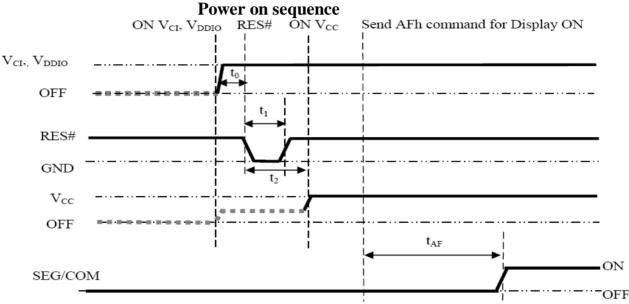

#### 5. TIMING OF POWER SUPPLY

# **♦**Power ON sequence:

- 1. Power ON V<sub>CI</sub>, V<sub>DDIO</sub>.

- 2. After  $V_{CI}$ ,  $V_{DDIO}$  becomes stable, set wait time at least 1ms ( $t_0$ ) for internal  $V_{DD}$  become stable. Then set RES# pin LOW (logic low) for at least 100us ( $t_1$ ) <sup>(4)</sup> and then HIGH (logic high).

- 3. After set RES# pin LOW (logic low), wait for at least 100us (t<sub>2</sub>). Then Power ON V<sub>CC</sub>. (1)

- 4. After  $V_{CC}$  become stable, send command AFh for display ON. SEG/COM will be ON after  $200 ms(t_{AF})$ .

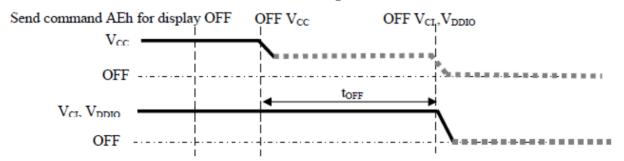

# **◆**Power OFF sequence:

- 1. Send command AEh for display OFF.

- 2. Power OFF V<sub>CC</sub>. (1), (2), (3)

- 3. Wait for  $t_{OFF}$ . Power OFF  $V_{CI}$ ,  $V_{DDIO}$  (where Minimum  $t_{OFF}$ =0ms (5), Typical  $t_{OFF}$ =100ms) **Power off sequence**

#### Note:

- $^{(1)}$  Since an ESD protection circuit is connected between  $V_{CI}$ ,  $V_{DDIO}$  and  $V_{CC}$ ,  $V_{CC}$  becomes lower than  $V_{CI}$  whenever  $V_{CI}$ ,  $V_{DDIO}$  is ON and  $V_{CC}$  is OFF as shown in the dotted line of  $V_{CC}$  in Figure above.

- <sup>(2)</sup>V<sub>CC</sub> should be kept float (disable) when it is OFF.

- (3) Power pins (V<sub>CI</sub>, V<sub>CC</sub>) can never be pulled to ground under any circumstance.

- <sup>(4)</sup> The register values are reset after  $t_1$ .

- (5) VCI, V<sub>DDIO</sub> should not be Power OFF before VCC Power OFF.

www.surenoo.com - 10 -

#### n ELECTRO-OPTICAL CHARACTERISTICS (Ta=25°C)

| Items            |       | Symbol  | Min.   | Тур.  | Max.   | Unit               | Remark                |  |

|------------------|-------|---------|--------|-------|--------|--------------------|-----------------------|--|

| Operating Lumi   | nance | L       | 40     | 50    | -      | cd /m <sup>2</sup> | Green                 |  |

| Power Consum     | ntion | P       |        | 400   | 400    | mW                 | 30% pixels ON         |  |

| Power Consum     | Г     | -       | 400    | 480   | 111 VV | $L=50cd/m^2$       |                       |  |

| Frame Freque     | Fr    | -       | 100    | ı     | Hz     | -                  |                       |  |

| Color Coordinate | Green | CIE x   | 0.270  | 0.310 | 0.350  | CIE1931            | Darkroom              |  |

| Color Coordinate | Gleen | CIE y   | 0.580  | 0.620 | 0.660  | CIE1931            | Darkiooni             |  |

| Pagnanga Tima    | Rise  | Tr      | -      | -     | 0.02   | ms                 | -                     |  |

| Response Time    | Decay | Td      | -      | -     | 0.02   | ms                 | -                     |  |

| Contrast Rati    | Cr    | 10000:1 | -      | ı     | 1      | Darkroom           |                       |  |

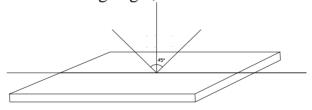

| Viewing Angle    | Δ θ   | 160     |        |       | Degree | -                  |                       |  |

| Operating Life 7 | Γime* | Top     | 45,000 |       | -      | Hours              | L=50cd/m <sup>2</sup> |  |

#### Note:

- **1.** 50cd/m<sup>2</sup> is based on  $V_{CI}=3.0V$ ,  $V_{CC}=16.0V$ , contrast command setting 0xDF;

- **2. Contrast ratio** is defined as follows:

**3. Life Time** is defined when the Luminance has decayed to less than 50% of the initial Luminance specification. (Odd and even chess board alternately displayed) (The initial value should be closed to the typical value after adjusting.)

www.surenoo.com - 11 -

# **n INTERFACE PIN CONNECTIONS**

| No        | Symbol    | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1         | NC        | No connection                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 2         | VSS       | Ground. Common Voltage Reference Pin                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 3         | VCC       | Power supply for panel driving voltage. Segment voltage                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 4         | VCOMH     | COM signal deselected voltage level. High Level Voltage Output Of COM Signal                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 5         | VLSS      | Analog system ground pin. Voltage Supply                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 6-13      | D7-D0     | These pins are bi-directional data bus connecting to the MCU data bus. Unused pins are recommended to tie LOW. (Except for D2 pin in SPI mode, D2 is pulled low in SPI mode).                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 14        | E (RD#)   | MCU Interface Input pin, in 6800 parallel mode, it is used as enable signal, read/write operation is initiated when this pin is set high with chip selected. In 8080 parallel mode, this pin receives read signal, read operation is initiated when this is pulled low with chip selected. When SPI interface is selected, this pin must be connected to ground.                                    |  |  |  |  |  |  |

| 15        | R/W#(WR#) | MCU Interface Input pin, in 6800 parallel mode, it is used as read/write selection input, read mode will be carried out when this pin is pulled high while write mode with this pin pulled low. In 8080 parallel mode, this pin will be write input, write operation is initiated when this is pulled low with chip selected. When SPI interface is selected, this pin must be connected to ground. |  |  |  |  |  |  |

| 16-<br>17 | BS0-1     | MCU bus interface selection pins. Select appropriate logic setting as described in the following table.    BS[1:0]   Bus Interface Selection                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 18        | DC#       | This pin is Data/Command control pin connected to the MCU. When the pin is pulled HIGH, the content at D[7:0] will be interpreted as data. When the pin is pulled LOW, the content at D[7:0] will be interpreted as command.                                                                                                                                                                        |  |  |  |  |  |  |

| 19        | CS#       | This pin is the chip select input connected to the MCU. The chip is enabled for MCU communication only when CS# is pulled LOW.                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 20        | RES#      | This pin is reset signal input. When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.                                                                                                                                                                                                                                                |  |  |  |  |  |  |

*www.surenoo.com* - 12 -

| 21 | FR                                                                                                      | This pin is No Connection pins. Nothing should be connected to this pin. This pin should be left open individually.                                |  |  |  |  |

|----|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 22 | IREF                                                                                                    | This pin is the segment output current reference pin. A resistor should be connected between this pin and VSS to maintain the current around 10uA. |  |  |  |  |

| 23 | NC                                                                                                      | No connection.                                                                                                                                     |  |  |  |  |

| 24 | VDDIO  Power supply for interface logic level. It should be match with the MCU interface voltage level. |                                                                                                                                                    |  |  |  |  |

| 25 | VDD                                                                                                     | Power supply pin for core logic operation. A capacitor is required to connect between this pin and VSS.                                            |  |  |  |  |

| 26 | VCI                                                                                                     | Low voltage power supply. VCI must always be equal to or higher than VDD and VDDIO.                                                                |  |  |  |  |

| 27 | VSL                                                                                                     | This is segment voltage reference pin. When external VSL is used, connect with resistor and diode to ground                                        |  |  |  |  |

| 28 | VLSS                                                                                                    | Analog system ground pin.                                                                                                                          |  |  |  |  |

| 29 | VCC                                                                                                     | Power supply for panel driving voltage. Segment Voltage                                                                                            |  |  |  |  |

| 30 | NC                                                                                                      | No Connection.                                                                                                                                     |  |  |  |  |

www.surenoo.com - 03 -

# n COMMAND TABLE

| D/C# | Hex          | D7 | D6                  | D5                  | D4                  | D3                  | D2                  | D2             | D0                  | Command                    | Descriptio                                                                                                                                                                                                                    |

|------|--------------|----|---------------------|---------------------|---------------------|---------------------|---------------------|----------------|---------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 00           | 0  | 0                   | 0                   | 0                   | 0                   | 0                   | 0              | 0                   | Enable Gray<br>Scale table | This command is sent to enable the Gray Scale table setting (command B8h)                                                                                                                                                     |

| 0    | 15           | 0  | 0                   | 0                   | 1                   | 0                   | 1                   | 0              | 1                   | Set Column                 | Set Column start and end address A[6:0]: Start                                                                                                                                                                                |

| 1    | A[6:0]       | *  | $A_6$               | $A_5$               | $A_4$               | $A_3$               | $A_2$               | $A_1$          | $A_0$               | Address                    | Address. [reset=0] B[6:0]: End Address.                                                                                                                                                                                       |

| 1    | B[6:0]       | *  | $B_6$               | $B_5$               | $B_4$               | $\mathbf{B}_3$      | $\mathbf{B}_2$      | $B_1$          | $B_0$               |                            | [reset=119] Range from 0 to 119                                                                                                                                                                                               |

| 0    | 5C           | 0  | 1                   | 0                   | 1                   | 1                   | 1                   | 0              | 0                   | Write RAM                  | Enable MCU to write Data into RAM                                                                                                                                                                                             |

|      |              | _  | _                   |                     |                     |                     | _                   |                |                     | Command                    |                                                                                                                                                                                                                               |

| 0    | 5D           | 0  | 1                   | 0                   | 1                   | 1                   | 1                   | 0              | 1                   | Read RAM                   | Enable MCU to read Data from RAM                                                                                                                                                                                              |

|      | 7.5          | 0  |                     | 1                   | 1                   | 0                   | 1                   | 0              |                     | Command<br>Set Row Address |                                                                                                                                                                                                                               |

| 0    | 75<br>A[6:0] | 0  | 1<br>A <sub>6</sub> | 1<br>A <sub>5</sub> | 1<br>A <sub>4</sub> | 0<br>A <sub>3</sub> | 1<br>A <sub>2</sub> | $0$ $A_1$      | 1<br>A <sub>0</sub> | Set Row Address            | Set Row start and end address Address. [reset=0] A[6:0]: Start B[6:0]: End Address.                                                                                                                                           |

| 1    | B[6:0]       | *  | B <sub>6</sub>      | B <sub>5</sub>      | B <sub>4</sub>      | B <sub>3</sub>      | B <sub>2</sub>      | B <sub>1</sub> | $B_0$               |                            | [reset=127] Range from 0 to 127                                                                                                                                                                                               |

|      |              |    | · ·                 | ,                   |                     |                     | _                   |                | Ü                   |                            |                                                                                                                                                                                                                               |

| 0    | A0           | 1  | 0                   | 1                   | 0                   | 0                   | 0                   | 0              | 0                   | Set Re-map and             | A[0]=0b, Horizontal address increment [reset] A[0]=1b,                                                                                                                                                                        |

| 1    | A[7:0]       | 0  | 0                   | A <sub>5</sub>      | $A_4$               | 0                   | $A_2$               | $A_1$          | A <sub>0</sub>      | Dual COM Line              | Vertical address increment  A[0]=10,                                                                                                                                                                                          |

| 1    | B[4]         | *  | *                   | 0                   | B <sub>4</sub>      | 0                   | 0                   | 0              | 1                   | mode                       | vortical address increment                                                                                                                                                                                                    |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | A[1]=0b, Disable Column Address Re-map [reset]                                                                                                                                                                                |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | A[1]=1b, Enable Column Address Re-map                                                                                                                                                                                         |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | A[2]=0b, Disable Nibble Re-map [reset] A[2]=1b,                                                                                                                                                                               |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | Enable Nibble Re-map                                                                                                                                                                                                          |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | A[4]=0b, Scan from COM0 to COM[N -1] [reset] A[4]=1b, Scan from COM[N-1] to COM0, where N is the Multiplex ratio                                                                                                              |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | A[5]=0b, Disable COM Split Odd Even [reset] A[5]=1b, Enable COM Split Odd Even                                                                                                                                                |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | $B[4], Enable / disable Dual COM Line mode \\ Disable Dual COM mode [reset] \\ Enable Dual COM mode (MUX \le 63) \\ \\$                                                                                                       |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | Note COM Split Odd Even mode                                                                                                                                                                                                  |

|      |              |    |                     |                     |                     |                     |                     |                |                     |                            | must be disabled (A[5]=0b) when enabling the Dual COM mode (B[4]=1b)                                                                                                                                                          |

| 0    | A1           | 1  | 0                   | 1                   | 0                   | 0                   | 0                   | 0              | 1                   | Set Display                | Set display RAM display start line register from 0-127                                                                                                                                                                        |

| 1    | A[6:0]       | *  | $A_6$               | $A_5$               | $A_4$               | $A_3$               | $A_2$               | $A_1$          | $A_0$               | Start Line                 | Display start line register is reset to 00h after RESET                                                                                                                                                                       |

| 0    | A2           | 1  | 0                   | 1                   | 0                   | 0                   | 0                   | 1              | 0                   | Sat Dieplay                | Set vertical scroll by COM from 0-127 The value                                                                                                                                                                               |

| 1    | A2<br>A[6:0] | *  | $A_6$               | A <sub>5</sub>      | $A_4$               | A <sub>3</sub>      | $A_2$               | A <sub>1</sub> | $A_0$               | Set Display<br>Offset      | is reset to 00H after RESET                                                                                                                                                                                                   |

|      | E            |    |                     |                     |                     |                     |                     |                |                     |                            |                                                                                                                                                                                                                               |

| 0    | A4~A7        | 1  | 0                   | 1                   | 0                   | 0                   | $X_2$               | $X_1$          | $X_0$               | Set Display<br>Mode        | A4h = Entire Display OFF, all pixels turns OFF in GS level 0<br>A5h = Entire Display ON, all pixels turns ON in GS level 15<br>A6h = Normal Display [reset] A7h = Inverse<br>Display (GS0 → GS15, GS1 → GS14, GS2 →<br>GS13,) |

www.surenoo.com - 14 -

| D/C# | Hex              | D7    | D6          | D5          | D4          | D3                               | D2          | D2          | D0          | Command                 | Descriptio                                                                                                           |  |  |

|------|------------------|-------|-------------|-------------|-------------|----------------------------------|-------------|-------------|-------------|-------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| 0    | A8               | 1     | 0           | 1           | 0           | 1                                | 0           | 0           | 0           | Enable Partial          | This command turns ON partial mode. The partial mode                                                                 |  |  |

| 1    | A[6:0]<br>B[6:0] | 0     | $A_6$ $B_6$ | $A_5$ $B_5$ | $A_4$ $B_4$ | A <sub>3</sub><br>B <sub>3</sub> | $A_2$ $B_2$ | $A_1$ $B_1$ | $A_0$ $B_0$ | Display                 | display area is defined by the following two parameters,<br>A[6:0]: Address of start row in the display area B[6:0]: |  |  |

|      | -[0.0]           |       | -0          | _,          |             | _,                               |             | _,          |             |                         | Address of end row in the display area, where B[6:0]                                                                 |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | must be $\geq$ A[6:0]                                                                                                |  |  |

| 0    | A9               | 1     | 0           | 1           | 0           | 1                                | 0           | 0           | 1           | Exit Partial            | This command is sent to exit the Partial Display mode                                                                |  |  |

|      |                  |       |             |             |             |                                  |             |             |             | Display                 |                                                                                                                      |  |  |

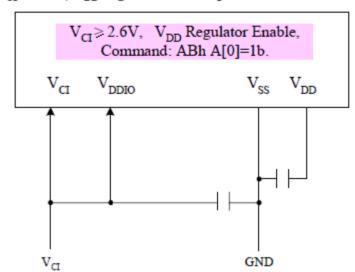

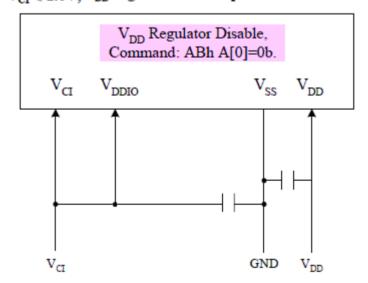

| 0    | AB               | 1     | 0           | 1           | 0           | 1                                | 0           | 1           | 1           | Function                | A[0]=0b, Select external V <sub>DD</sub>                                                                             |  |  |

| 1    | A[0]             | 0     | 0           | 0           | 0           | 0                                | 0           | 0           | $A_0$       | Selection               | A[0]=1b, Enable internal V <sub>DD</sub> regulator [reset]                                                           |  |  |

| 0    | AE~AF            | 1     | 0           | 1           | 0           | 1                                | 1           | 1           | $X_0$       | Set Sleep mode          | AEh = Sleep mode ON (Display OFF) AFh =                                                                              |  |  |

|      | 7112-711         | 1     | O           | 1           |             | 1                                | 1           | 1           | 210         | ON/OFF                  | Sleep mode OFF (Display ON)                                                                                          |  |  |

| 0    | B1               | 1     | 0           | 1           | 1           | 0                                | 0           | 0           | 1           | Set Phase               | A[3:0] Phase 1 period (reset phase length) of 5~31 DCLK(s)                                                           |  |  |

| 1    | A[7:0]           | $A_7$ | $A_6$       | $A_5$       | $A_4$       | $A_3$                            | $A_2$       | $A_1$       | $A_0$       | Length                  | clocks as follow:                                                                                                    |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | A[3:0] Phase 1 period                                                                                                |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         |                                                                                                                      |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0000 invalid                                                                                                         |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0001 invalid                                                                                                         |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0010 5 DCLKs                                                                                                         |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0011 7 DCLKs                                                                                                         |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0100 9 DCLKs [reset]                                                                                                 |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | : :                                                                                                                  |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 1111 31 DCLKs                                                                                                        |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | TITE ST BOLKS                                                                                                        |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | A[7:4] Phase 2 period (first pre-charge phase length) of 3~15 DCLK(s) clocks as follow:                              |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | A[7:4] Phase 2 period                                                                                                |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0000 invalid                                                                                                         |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0001 invalid                                                                                                         |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0010 invalid                                                                                                         |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         |                                                                                                                      |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0011 3 DCLKs                                                                                                         |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | : :                                                                                                                  |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0111 7 DCLKs [reset]                                                                                                 |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | : :                                                                                                                  |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 1111 15 DCLKs                                                                                                        |  |  |

| 0    | В3               | 1     | 0           | 1           | 1           | 0                                | 0           | 1           | 1           | Set Front Clock         | A[3:0] [reset=0], divide by DIVSET where                                                                             |  |  |

| 1    | A[7:0]           | $A_7$ | $A_6$       | $A_5$       | $A_4$       | $A_3$                            | $A_2$       | $A_1$       | $A_0$       | Divider /               |                                                                                                                      |  |  |

|      |                  |       |             |             |             |                                  |             |             |             | Oscillator<br>Frequency | A[3:0] DIVSET                                                                                                        |  |  |

|      |                  |       |             |             |             |                                  |             |             |             | 1                       | 0000 divide by 1                                                                                                     |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0001 divide by 2                                                                                                     |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0010 divide by 4                                                                                                     |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0011 divide by 8                                                                                                     |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0100 divide by 16                                                                                                    |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0101 divide by 32                                                                                                    |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0110 divide by 64                                                                                                    |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 0111 divide by 128                                                                                                   |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         |                                                                                                                      |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | <u> </u>                                                                                                             |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 1001 divide by 512                                                                                                   |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | 1010 divide by 1024                                                                                                  |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | >=1011 invalid                                                                                                       |  |  |

|      |                  |       |             |             |             |                                  |             |             |             |                         | A[7:4] Oscillator frequency, frequency increases as level                                                            |  |  |

|      |                  |       |             |             | <u> </u>    | <u> </u>                         | l           | 1           | <u> </u>    |                         | increases [reset=0101b]                                                                                              |  |  |

*www.surenoo.com* - 15 -

| <b>D</b> /C# | Hex                  | <b>D</b> 7                           | D6                                   | D5                                   | D4                                   | D3                                   | D2                                   | D2                                   | D0                                   | Command                       | Descriptio                                                                                      |  |  |

|--------------|----------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------|--|--|

| 0            | B4                   | 1                                    | 0                                    | 1                                    | 1                                    | 0                                    | 1                                    | 0                                    | 0                                    | Display                       | A[1:0] = 00b: Enable external VSL $A[1:0] = 10b$ :                                              |  |  |

| 1<br>1       | A[1:0]<br>B[7:3]     | 1<br>B <sub>7</sub>                  | $0 \\ B_6$                           | 1<br>B <sub>5</sub>                  | $0$ $B_4$                            | 0<br>B <sub>3</sub>                  | 0<br>1                               | $A_1$ 0                              | A <sub>0</sub> 1                     | Enhancement A                 | Internal VSL [reset] B[7:3] = 11111b: Enhanced low GS display quality B[7:3] = 10110b: Normal   |  |  |

|              |                      |                                      |                                      | -                                    |                                      |                                      |                                      |                                      |                                      |                               | [reset]                                                                                         |  |  |

| 0            | B5                   | 1                                    | 0                                    | 1                                    | 1                                    | 0                                    | 1                                    | 0                                    | 1                                    | Set GPIO                      | A[1:0] GPIO0: 00 pin HiZ, Input disabled 01 pin HiZ,                                            |  |  |

| 1            | A[3:0]               | *                                    | *                                    | *                                    | *                                    | $A_3$                                | $A_2$                                | $A_1$                                | $A_0$                                |                               | Input enabled 10 pin output LOW [reset] 11 pin output HIGH                                      |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               |                                                                                                 |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | A[3:2] GPIO1: 00 pin HiZ, Input disabled 01 pin HiZ, Input enabled 10 pin output LOW            |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | [reset] 11 pin output HIGH                                                                      |  |  |

| 0            | В6                   | 1                                    | 0                                    | 1                                    | 1                                    | 0                                    | 1                                    | 1                                    | 0                                    | Set Second                    | A[3:0] Second Pre-charge period                                                                 |  |  |

| 1            | A[3:0]               | *                                    | *                                    | *                                    | *                                    | $A_3$                                | $A_2$                                | $A_1$                                | $A_0$                                | Precharge<br>Period           | 0000b 0 dclk<br>0001b 1 dclk                                                                    |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               |                                                                                                 |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | 000b 8 dclks [reset]                                                                            |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | 1111b 15 dclks                                                                                  |  |  |

| 0            | B8                   | 1                                    | 0                                    | 1                                    | 1                                    | 1                                    | 0                                    | 0                                    | 0                                    | Set Gray Scale                | The next 15 data bytes define Gray Scale (GS) Table by                                          |  |  |

| 1<br>1       | A1[7:0]<br>A2[7:0]   | A1 <sub>7</sub><br>A2 <sub>7</sub>   | A1 <sub>6</sub><br>A2 <sub>6</sub>   | A1 <sub>5</sub><br>A2 <sub>5</sub>   | A1 <sub>4</sub><br>A2 <sub>4</sub>   | A1 <sub>3</sub><br>A2 <sub>3</sub>   | A1 <sub>2</sub><br>A2 <sub>2</sub>   | A1 <sub>1</sub><br>A2 <sub>1</sub>   | A1 <sub>0</sub><br>A2 <sub>0</sub>   | Table                         | setting the gray scale pulse width in unit of DCLK's (ranges from 0d ~ 180d)                    |  |  |

| 1<br>1       |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | A1[7:0]: Gamma Setting for GS1,<br>A2[7:0]: Gamma Setting for GS2,                              |  |  |

| 1<br>1       | A14[7:0]             | A14 <sub>7</sub>                     | A14 <sub>6</sub>                     | A14 <sub>5</sub>                     | A14 <sub>4</sub>                     | A14 <sub>3</sub>                     | A14 <sub>2</sub>                     | A14 <sub>1</sub>                     | A14 <sub>0</sub>                     |                               | :<br>A14[7:0]: Gamma Setting for GS14,                                                          |  |  |

| 1            | A14[7:0]<br>A15[7:0] | A14 <sub>7</sub><br>A15 <sub>7</sub> | A14 <sub>6</sub><br>A15 <sub>6</sub> | A14 <sub>5</sub><br>A15 <sub>5</sub> | A14 <sub>4</sub><br>A15 <sub>4</sub> | A14 <sub>3</sub><br>A15 <sub>3</sub> | A14 <sub>2</sub><br>A15 <sub>2</sub> | A14 <sub>1</sub><br>A15 <sub>1</sub> | A14 <sub>0</sub><br>A15 <sub>0</sub> |                               | A14[7:0]: Gamma Setting for GS14,<br>A15[7:0]: Gamma Setting for GS15                           |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | Note  Note  Setting of GS1 / Setting of GS2 / Setting of GS3                                    |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | (1) 0 ≤ Setting of GS1 < Setting of GS2 < Setting of GS3<br>< Setting of GS14 < Setting of GS15 |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | (2) The setting must be followed by the Enable Gray Scale Table command (00h)                   |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | ` /                                                                                             |  |  |

| 0            | В9                   | 1                                    | 0                                    | 1                                    | 1                                    | 1                                    | 0                                    | 0                                    | 1                                    | Select Default<br>Linear Gray | The default Linear Gray Scale table is set in unit of DCLK's as follow                          |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      | Scale table                   | GS0 level pulse width = 0;                                                                      |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | GS1 level pulse width = 0;<br>GS2 level pulse width = 8;                                        |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | GS3 level pulse width = 16;                                                                     |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               |                                                                                                 |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | GS14 level pulse width = 104;<br>GS15 level pulse width = 112;                                  |  |  |

| 0            | BB                   | 1                                    | 0                                    | 1                                    | 1                                    | 1                                    | 0                                    | 1                                    | 1                                    | Set Pre-charge                | Set pre-charge voltage level.[reset = 17h]                                                      |  |  |

| 1            | A[4:0]               | *                                    | *                                    | *                                    | $A_4$                                | $A_3$                                | $A_2$                                | $A_1$                                | $A_0$                                | voltage                       | A[4:0] Hex code pre-charge voltage                                                              |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | 00000 00h 0.20 x Vcc                                                                            |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | : : :                                                                                           |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | 11111 1Fh 0.60 x Vcc                                                                            |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               |                                                                                                 |  |  |

| 0            | BE                   | 1 *                                  | 0 *                                  | 1                                    | 1                                    | 1                                    | 1                                    | 1                                    | 0                                    | Set V <sub>COMH</sub>         | Set COM deselect voltage level [reset = 04h]                                                    |  |  |

| 1            | A[2:0]               | *                                    | *                                    | *                                    | *                                    | 0                                    | $A_2$                                | $A_1$                                | $A_0$                                |                               | A[2:0] Hex code V COMH                                                                          |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | 000 00h 0.72 x VCC                                                                              |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | : : :                                                                                           |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | 100 04h 0.80 x VCC [reset]                                                                      |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | : : :                                                                                           |  |  |

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               | 111 07h 0.86 x VCC                                                                              |  |  |

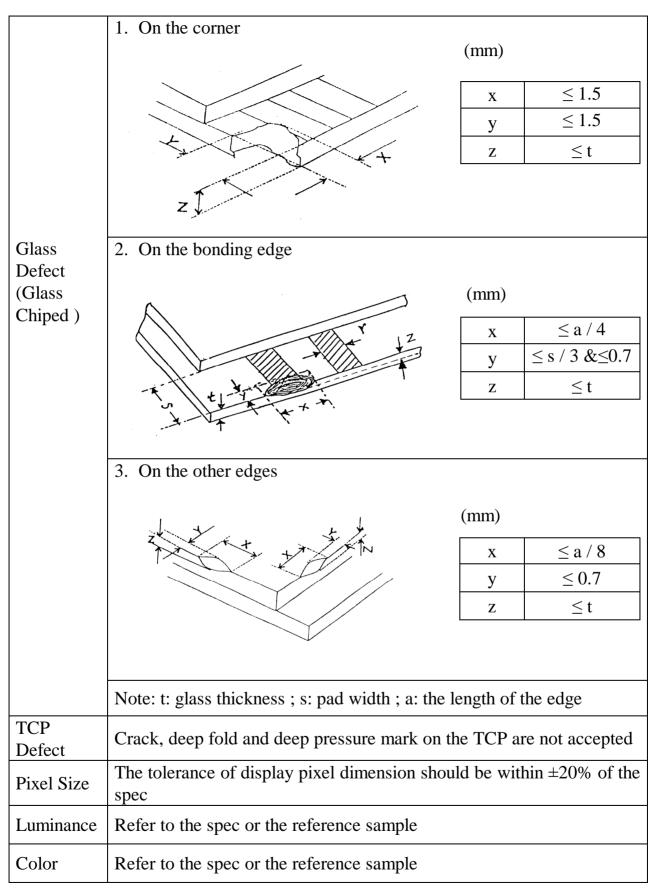

|              |                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                                      |                               |                                                                                                 |  |  |